基于DSP的高速数据采集系统硬件设计

[09-08 11:42:37] 来源:http://www.88dzw.com 其它电路 阅读:8208次

文章摘要: ADS5422是14 bit的最高采样频率可达62 MSPs的高速AD转换芯片,采用单-5 V电源供电,在采样频率为10 MHz时其最大动态范围为82 dB,最高信噪比达到72 dB,其数字量输出可以直接和5 V或者3.3 V的CMOS芯片连接,模拟量输入的峰峰值为4 V,可以直接输入0.5~4.5 V的模拟量,封装形式为64脚的扁平四方封装。 AD可以接受3 V或者5 V的TTL或者CMOS电平。DSP可以为AD转换器提供时钟信号,并且可以软件设置输入时钟的各种特征量,包括时钟频率、高电平宽度等,基本上可以满足AD5422对时钟信号的要求。www.88dzw.com

基于DSP的高速数据采集系统硬件设计,标签:电路设计,http://www.88dzw.comADS5422是14 bit的最高采样频率可达62 MSPs的高速AD转换芯片,采用单-5 V电源供电,在采样频率为10 MHz时其最大动态范围为82 dB,最高信噪比达到72 dB,其数字量输出可以直接和5 V或者3.3 V的CMOS芯片连接,模拟量输入的峰峰值为4 V,可以直接输入0.5~4.5 V的模拟量,封装形式为64脚的扁平四方封装。

AD可以接受3 V或者5 V的TTL或者CMOS电平。DSP可以为AD转换器提供时钟信号,并且可以软件设置输入时钟的各种特征量,包括时钟频率、高电平宽度等,基本上可以满足AD5422对时钟信号的要求。 www.88dzw.com

ADS5422芯片内部结构框图如图2所示。

A/D的模拟信号输入可以采用单端输入方式和差分输入方式两种。两种方式比较,单端输入方式接线简单,但抗噪性能差,而差分输入方式具有较强的抗噪能力,这样可以尽量减少信号噪声以及电磁干扰。

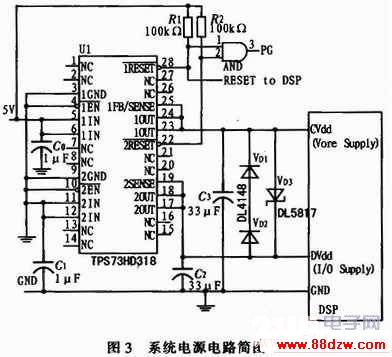

2.2 DSP电源设计

TMS320VC5509芯片DSP采用低电压分离式供电方式进行供电,这样可以大大降低DSP芯片的功耗。其中芯片内核采用1.8 V电压供电,外部I/O采用3.3 V电压供电。据此可以选择TI公司的TPS73HD318芯片,该芯片是双路输出低压降(LDO)稳压器,最大电流750 mA,可以将TPS7 0451的双输出配置成两路不同的输出,分别输出1.8 V和3.3 V的电压,图3为系统的电源电路简图。

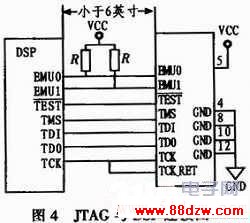

2.3 JTAG电路

JTAG是基于IEEE 1149.1标准的一种边界扫描测试方式(Boundary-sCAN Test),结合仿真器和仿真软件,可访问DSP的所有资源,包括片内寄存器以及所有的存储器,从而提供实时的硬件仿真与调试环境,便于开发人员进行系统调试。在大多数情况下,如果开发板和仿真器之间的连接电缆不超过6英寸,可以采用图4的接法。但应该注意,DSP的EMU0和EMU1引脚都需要上拉电阻,推荐值为4.7 kΩ或者10 kΩ。如果DSP和仿真器之间的连接电缆超过6英寸,则需要另加缓冲驱动电路。

2.4 时钟电路

TMS320VC5509的外部时钟从CLKIN引脚输入,在内部修改这个信号,来产生希望频率的输出时钟,时钟发生器将这个输出时钟(即CPU时钟)送给CPU、外设和其他的内部模块。也可以用可编程的时钟分频器对CPU时钟分频,在CLKOUT引脚输出。时钟发生器中还有一个时钟模式寄存器(CLKMD),用来控制和监视时钟发生器,它可以控制时钟发生器进入两种工作模式:

1)旁路模式,PLL被旁路掉,输出时钟的频率就等于输入时钟的频率除以1、2、4。

2)锁定模式,输入时钟既可以乘以或除以一个系数来获得期望的输出频率,并且输出时钟相位与输入信号锁定。

在锁定模式下,输出频率由下面的公式计算:

输出频率=(PLL MULT/(PLL DIV+1))×输入时钟频率

在此,可以选择时钟发生器工作在锁定模式,即CLKMD的PLL ENABLE为1,外部振荡晶体可以为10~20 MHz。根据外部振荡晶体与DSP内部时钟信号,可以计算出相应的PLLMULT与PLL DIV值,图5为DSP的外部时钟电路。

- 上一篇:动态称重信号采集系统设计

《基于DSP的高速数据采集系统硬件设计》相关文章

- › 基于DSP的混合信号解决方案解决高级音频处理难题

- › 基于DS3231的高精度时钟接口设计

- › 基于DSPIC30F4011单片机的CAN总线通信设计

- › 基于DSP的高速数据采集系统硬件设计

- 在百度中搜索相关文章:基于DSP的高速数据采集系统硬件设计

- 在谷歌中搜索相关文章:基于DSP的高速数据采集系统硬件设计

- 在soso中搜索相关文章:基于DSP的高速数据采集系统硬件设计

- 在搜狗中搜索相关文章:基于DSP的高速数据采集系统硬件设计

当前位置:

当前位置: