动态称重信号采集系统设计

[09-08 11:42:35] 来源:http://www.88dzw.com 其它电路 阅读:8638次

文章摘要:www.88dzw.com1.3 PSoC器件 CY8C24794 CY8C24794包括一个全速(12 Mbps)USB2.0SIE(含有一个精度达0.25%的准确时钟和一个符合USB2.0定时规范的集成振荡器),且不需要外部晶体,因而减少了元件和引脚数目。该器件提供了4个单向端点和1个双向控制端点,以支持控制型、中断型、等时型和成批型传输以及灵活的同步处理。它提供了多达48个模拟输入,除了6个标准PSoC可配置模拟块和4个数字块之外,它还提供了16 kb快闪程序存储器、1 kb SRAM数据存储器和一个至专用256 b缓冲器的易用型8通道DMA(供USB SIE之用)。 CY8

动态称重信号采集系统设计,标签:电路设计,http://www.88dzw.comwww.88dzw.com

1.3 PSoC器件

CY8C24794 CY8C24794包括一个全速(12 Mbps)USB2.0SIE(含有一个精度达0.25%的准确时钟和一个符合USB2.0定时规范的集成振荡器),且不需要外部晶体,因而减少了元件和引脚数目。该器件提供了4个单向端点和1个双向控制端点,以支持控制型、中断型、等时型和成批型传输以及灵活的同步处理。它提供了多达48个模拟输入,除了6个标准PSoC可配置模拟块和4个数字块之外,它还提供了16 kb快闪程序存储器、1 kb SRAM数据存储器和一个至专用256 b缓冲器的易用型8通道DMA(供USB SIE之用)。

CY8C24794得到了开发软件的支持,从而能够在不到1小时的时间里完成基本实现方案的构建。该软件包括一个用户模块,可使设计方案得以快速实现。这种USBFS协议用户模块可生成旨在实现简易型开发的应用程序设计接口(API),并包括一个设置向导。该用户模块及其对应的API在用户模块数据表中进行了清晰的说明。还包括一个带向导的HID模块。

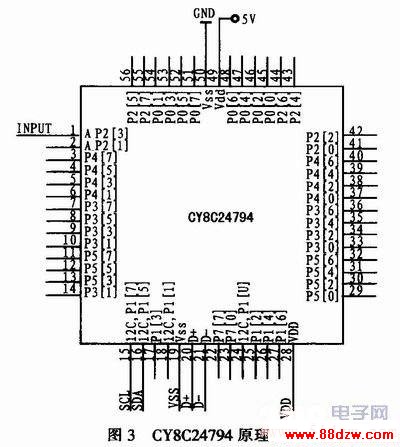

CY8C24794采用56引脚(8 mmx8 mm)MLF封装。其工作电压范围为3.0~5.25 V,工作温度范围为-40~85℃,批量购买时的单价不到2.00美元。

此模块主要实现以下几个功能:1)对电荷放大器转换后的电压信号进行放大滤波;2)将滤波后的模拟信号进行AD转换,变成计算机能够处理的数字信号;3)将转换后的信号通过其内含的USB接口传送到计算机上。从实现的功能和价格等方面考虑,所以CY8C24794是最合理的选择。

根据以上几个功能可以将CY8C24794配置成放大器、低通滤波器、AD和USB接口。CY8C24794的原理图如图3所示,信号从INPUT输入,从D+、D-输出,SCL和SDA为芯片的动态配置引脚。

2 PSoC内部资源配置

赛普拉斯半导体公司宣布推出业界首款也是唯一在单个封装中包括无代码与高级语言编程模式的集成设计环境PSoC Designer 5.0。赛普拉斯将其革命性的PSoC Express可视化嵌入式系统设计工具与功能齐全的PSoC Designer软件进行完美结合,创建了一个全新的设计范例。现在用户可以在拖放式可视化设计模式(系统级浏览)下开始项目设计,然后移入C语言(芯片级浏览)进行基于代码的设计,以精调并定制他们的项目,而所有这些步骤均可用一个PSoC Designer 5.0工具来完成。PSoC设计必须先完成芯片内部资源规划,其具体流程为:确定系统需求、选择用户模块、放置用户模块、设置全局变量和用户模块参数、定义输出引脚、产生应用代码、编辑应用代码。

本系统所配置主要包括以下几个用户模块:PGA模块、LPF模块、A/D模块和USB模块。配置的内部硬件资源包括2个数字模块:Counter16、ADCI NC1 2—1和3个模拟模块LPF1、CMPP RG-1、PGA。

PSoC全局资源配置如图4所示。PSoC用户模块参数设置及内部硬件资源配置如图5所示。

图中上面一部分主要是AD数字部分的配置,利用了两个数字模块,图的下方主要是滤波器和放大器部分的配置,放大器利用了一个模拟模块,滤波器利用了两个模拟模块,AD也使用了一个模拟模块。将它们的接口分别于内部的模块相连即完成了配置。用户模块的参数设置:PGA模块设置的参数Gain为48,LPF模块设置如图6所示。

Tag:其它电路,电路设计,家电维修 - 单元电路介绍 - 其它电路

《动态称重信号采集系统设计》相关文章

- › 动态称重信号采集系统设计

- 在百度中搜索相关文章:动态称重信号采集系统设计

- 在谷歌中搜索相关文章:动态称重信号采集系统设计

- 在soso中搜索相关文章:动态称重信号采集系统设计

- 在搜狗中搜索相关文章:动态称重信号采集系统设计

最新更新

当前位置:

当前位置: