基于赛灵思FPGA的硬件加速技术打造高速系统

[10-10 20:38:44] 来源:http://www.88dzw.com 其它电路 阅读:8994次

文章摘要:最后一个回合稍有不同,因为其中省略了一些步骤。加密过程采用所谓的S 盒(其提供非线性)执行替代。我们可以把它安置到一个 16×16×8 位矩阵中,从而能够适应常见的赛灵思 BRAM原语。多个 S 盒实例可以加速 IP 核并在适当的位置为内核提供所需数据,而无需等待对主存储器的长时间总线存取。解密过程大同小异,其采用相同密钥,但方向相反,并且使用不同 S 盒。快 12 倍在加密和解密中,大部分运算按行或列执行,剩下四项运算并行计算 —而硬件对此任务得心应手。这样就能够通过不同来源实现 AES 硬件的各个部分。为了加速系统,我们从庞大、快速增长的 OpenCor

基于赛灵思FPGA的硬件加速技术打造高速系统,标签:电路设计,http://www.88dzw.com最后一个回合稍有不同,因为其中省略了一些步骤。加密过程采用所谓的S 盒(其提供非线性)执行替代。我们可以把它安置到一个 16×16×8 位矩阵中,从而能够适应常见的赛灵思 BRAM原语。多个 S 盒实例可以加速 IP 核并在适当的位置为内核提供所需数据,而无需等待对主存储器的长时间总线存取。解密过程大同小异,其采用相同密钥,但方向相反,并且使用不同 S 盒。

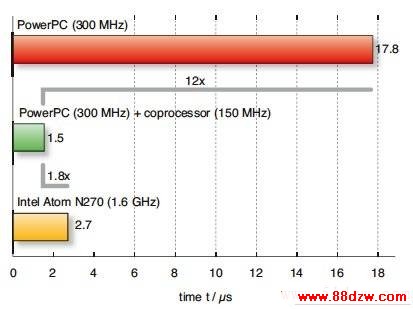

快 12 倍

在加密和解密中,大部分运算按行或列执行,剩下四项运算并行计算 —而硬件对此任务得心应手。这样就能够通过不同来源实现 AES 硬件的各个部分。为了加速系统,我们从庞大、快速增长的 OpenCores.org 资源库获取AES 内核。

我们删除了原有的总线接口(因为它适用于另一种 FPGA 架构),另外为APU 添加了一个接口,以便把 AES 内核作为 FCM 协处理器连接到 PowerPC上。我们共使用 8 个所谓的 UDI 指令在PowerPC 和 AES FCM 之间传输数据。工作结果非常令人满意( 见图2) 。硬件加速的系统比原实现快了12 倍。原来用以 300 MHz运行的独立的 PowerPC 加密一个单块需要 17.8微秒,而采用以 150 MHz 运行的 AESFCM 只需 1.5 微秒。如果只以升级到速度稍快的 CPU来加速运算,我们采用硬件加速后的 1.5 微秒速度表现超过基于 Intel Atom 1.6-GHz CPU 的纯软件实现(其需要 2.7 微秒)。上述结果证明了使用 FPGA 技术的硬件加速的卓越潜能。

图 2 — 硬件加速系统(中间绿条)快于独立的 PowerPC 或 Atom 处理器。

Tag:其它电路,电路设计,家电维修 - 单元电路介绍 - 其它电路

《基于赛灵思FPGA的硬件加速技术打造高速系统》相关文章

- › 基于赛灵思FPGA的硬件加速技术打造高速系统

- 在百度中搜索相关文章:基于赛灵思FPGA的硬件加速技术打造高速系统

- 在谷歌中搜索相关文章:基于赛灵思FPGA的硬件加速技术打造高速系统

- 在soso中搜索相关文章:基于赛灵思FPGA的硬件加速技术打造高速系统

- 在搜狗中搜索相关文章:基于赛灵思FPGA的硬件加速技术打造高速系统

最新更新

当前位置:

当前位置: