用于PCB品质验证的时域串扰测量法分析

[09-12 18:53:05] 来源:http://www.88dzw.com PCB设计 阅读:8804次

文章摘要:图6:前向串扰的测量。如果互电感比互电容耦合的串扰大,那么在干扰脉冲的上升沿处串扰脉冲应为负,宽度等于干扰脉冲的上升时间。图中仪器显示的就是一个幅度为48.45 mV的负脉冲(C4)。干扰脉冲幅度为250 mV,而串扰幅度将近50 mV,因此该干扰脉冲的快速边沿在被干扰线上产生了20%的串扰。见图7。图7:测量得到的前向串扰。由于测量时来自80E04的输入阶跃电压具有非常快的边沿,因而得到的串扰过大,并不能代表实际逻辑电路中的驱动信号。例如,如果驱动信号来自一个1.5 ns的CMOS门,产生的串扰脉冲就更宽,幅度也更小。要使测量能够体现出这种情况,可利用仪器的定义算法(Define Math)

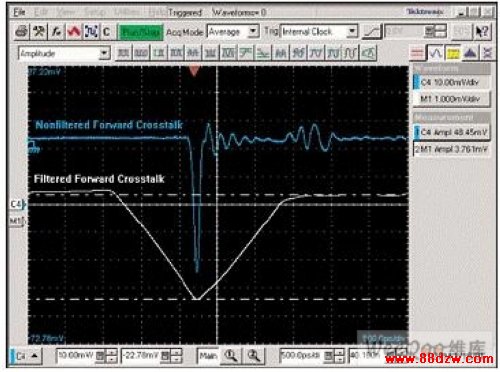

用于PCB品质验证的时域串扰测量法分析,标签:pcb培训,pcb是什么,pcb软件,http://www.88dzw.com图6:前向串扰的测量。

如果互电感比互电容耦合的串扰大,那么在干扰脉冲的上升沿处串扰脉冲应为负,宽度等于干扰脉冲的上升时间。图中仪器显示的就是一个幅度为48.45 mV的负脉冲(C4)。干扰脉冲幅度为250 mV,而串扰幅度将近50 mV,因此该干扰脉冲的快速边沿在被干扰线上产生了20%的串扰。见图7。

图7:测量得到的前向串扰。

由于测量时来自80E04的输入阶跃电压具有非常快的边沿,因而得到的串扰过大,并不能代表实际逻辑电路中的驱动信号。例如,如果驱动信号来自一个1.5 ns的CMOS门,产生的串扰脉冲就更宽,幅度也更小。要使测量能够体现出这种情况,可利用仪器的定义算法(Define Math)功能在信号捕获之后增加一个低通滤波器。图7中的M1波形(白色)给出的就是经滤波后的测量结果。需要注意的是M1在垂直方向比未经滤波的波形敏感10倍。

尽管数学分析已经证明,信号捕获后进行低通滤波这种技术的效果与对连接到线上的干扰脉冲进行物理滤波的效果是相同的,但以下几步测量却更有说服力:

>测量由两个上升沿一快一慢而幅度相同的干扰脉冲导致的串扰,

>然后将上升沿快的干扰脉冲导致的串扰通过低通滤波变至慢上升沿干扰脉冲的串扰,最后检查结果。

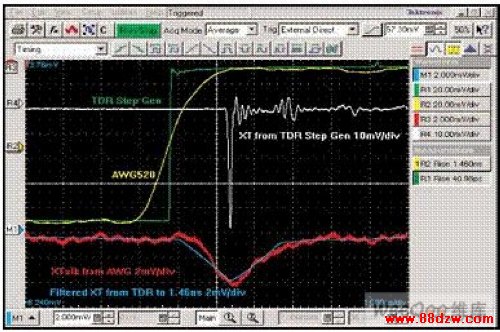

图8给出了仪器上显示的测量结果:

图8:前向串扰的后滤。

>$波形(R2)是慢沿干扰脉冲,红色波形(R3)是由它导致的串扰。

>绿色波形是快沿TDR脉冲(R1),白色波形(R4)是由它导致的串扰。

>蓝色波形是由白色波形滤波后减缓了脉冲上升沿得到的波形,它代表的就是对串扰进行后滤波的结果。图中显示的红色和蓝色两个串扰波形是以相同的电压刻度显示的。

反向串扰测量

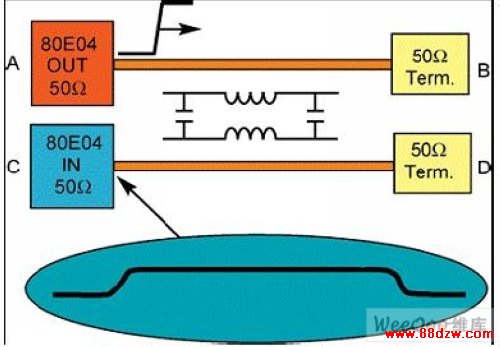

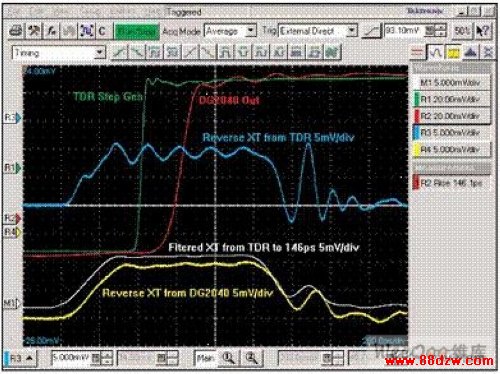

图9:反向串扰的测量。

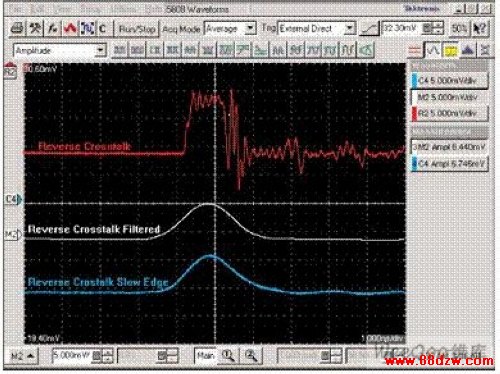

单测反向串扰时,需将干扰线与被干扰线均端接一个50 欧姆的电阻以消除反射。测量应在被干扰线的左端进行,如图9所示。反射脉冲的幅度很低,宽度是线长的两倍,因为在走线末端的串扰必定要传回走线源端。图??显示的是反向串扰的测量情况,图中快沿干扰脉冲产生的串扰约为?? mV,相当于干扰脉冲幅度的4%。反向串扰的幅度与干扰脉冲的上升时间无关。图10中,下面两个波形为慢沿脉冲产生的串扰和快沿脉冲产生的串扰经后滤波得到的波形,它们的幅度都是6.5 mV。走线线长与干扰脉冲上升时间的差距使得慢沿脉冲产生的反向串扰幅度较小。

图10:测量得到的反向串扰。

因为此时干扰脉冲的上升时间要大于走线的线长,故脉冲边沿沿走线方向回传到走线源端时还未到达幅度顶点。图11所示为利用一台200 ps上升时间发生器(DG2040)和80E04采样模块的17 ps发生器的输出作为干扰脉冲时得到的串扰测量结果。图中显示的3个串扰波形均采用5 mV/div的电压刻度。

《用于PCB品质验证的时域串扰测量法分析》相关文章

- › 用于PCB品质验证的时域串扰测量法分析

- 在百度中搜索相关文章:用于PCB品质验证的时域串扰测量法分析

- 在谷歌中搜索相关文章:用于PCB品质验证的时域串扰测量法分析

- 在soso中搜索相关文章:用于PCB品质验证的时域串扰测量法分析

- 在搜狗中搜索相关文章:用于PCB品质验证的时域串扰测量法分析

当前位置:

当前位置: