用matlab来实现fpga功能的设计

[11-20 16:14:30] 来源:http://www.88dzw.com FPGA 阅读:8752次

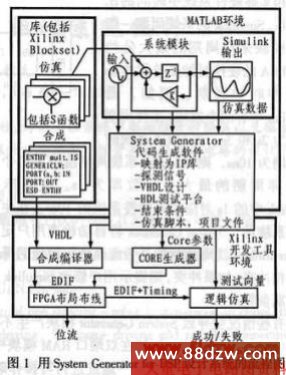

文章摘要: 在Matlab中,我们可以通过simulink的库浏览器使用Xilinx blockset库中的模块,Xilinx blockset库中的模块可以与simulink其它库中的模块自由组合。Xilinx blockset库中最重要的模块是System Generator,利用该模块可完成系统级设计到基于FPGA的底层硬件设计的转换工作。可以在System Generator模块的属性对话框中选择目标FPGA器件、目标系统时钟周期等选项。System Generator将Xilinx blockset中的模块映射为IP库中的模块,接着从系统参数(例如采样周期)推断出控制信号和电路,

用matlab来实现fpga功能的设计,标签:fpga是什么,fpga教程,http://www.88dzw.com

在Matlab中,我们可以通过simulink的库浏览器使用Xilinx blockset库中的模块,Xilinx blockset库中的模块可以与simulink其它库中的模块自由组合。Xilinx blockset库中最重要的模块是System Generator,利用该模块可完成系统级设计到基于FPGA的底层硬件设计的转换工作。可以在System Generator模块的属性对话框中选择目标FPGA器件、目标系统时钟周期等选项。System Generator将Xilinx blockset中的模块映射为IP库中的模块,接着从系统参数(例如采样周期)推断出控制信号和电路,再将simulink的分层设计转换为VHDL的分层网表,之后,System Generator即可调用Xilinx CORE Generator和VHDL模拟、综合、实现工具来完成硬件设计。

由于一般的FPGA综合工具不支持浮点数,因此System Generator模块使用的数据类型为任意精度的定点数,这样可以实现准确的硬件模拟。由于smulink中的信号类型是双精度浮点数,因此在xil-inx模块和非Xilinx模块之间必须插入gateway inblock和gateway inblock模块。通常simulink中的连续时间信号在Gateway In block模块中进行采样,同时该模块也可将双精度浮点信号转换为定点信号,而Gateway Out block模块则可将定点信号转换为双精度浮点信号。大部分xilinx模块能够根据输入信号类型推断输出信号的类型。如果模块的精度参数定义为全精度,则模块将自动选择输出信号类型以保证不损失输入信号精度,并自动进行符号位扩展和补零操作。用户也可以自定义输出信号类型来进行精度控制。

3、使用中需注意的问题

在FPGA系统设计中,时钟的设计十分重要。因此必须正确理解System Generator中的时钟和FPGA硬件时钟之间的关系。simulink中没有明确的时钟源信号,模块在系统参数中定义的采样周期点进行采样。硬件设计中的外部时钟源对时序逻辑电路十分重要。在System Generator模块中,通过定义simulink System period和fpga system clock period参数可以建立simulink采样周期和硬件时钟间的关系,也可通过设置这些参数来改变Simulink中模拟时间和实际硬件系统中时间的比例关系。simulink的系统周期一般是各模块采样周期的最大公约数。FPGA的硬件时钟是单位为ns的硬件时钟周期。例如,若simulink中有两个模块,采样周期分别为2s和3s,而FPGA系统时钟周期为10ns,则simulink系统周期应该为两个模块采样周期的最大公约数即为1s。这意味着simulink中的1s对应实际硬件系统的10ns。在生成硬件系统前,System Generator将自动检查用户定义的simulink系统周期参数是否与系统中模块的采样周期相冲突,如果冲突,则提示用修改Simulink系统周期参数。

有些情况会导致System Generator模块产生不确定数(NaN-not a number)。如在双端口ram模块中,两个端口同时对模块中的某一地址进行写操作时,该地址中的数据将被标记为NaN。如果模块中有不确定数出现,则表明该模块的最终硬件实现将会有不可预测的行为,当simulink进行仿真时,System Generator将会捕捉该错误。

4、应用实例

图2是一个图像处理应用实例的系统实现框图。该应用实例使用5×5的二维FIR滤波器完成图像增强预处理。该系统将输入图像分别延迟0×N(N为输入图像宽度)、1×N、2×N、3×N、4×N个采样点后输入5个Line Buffer,数据在Line Buffer中缓存后并行输入5个5抽头的MAC FIR滤波器。滤波器系统存储于FPGA的块RAM中,图像数据经滤波器处理后输出。图3为Line Buffer实现框图,图4为5×5滤波器框图。

《用matlab来实现fpga功能的设计》相关文章

- › VB调用Matlab在WEDM仿真系统中的应用

- › 用matlab来实现fpga功能的设计

- › 用MATLAB设计FIR滤波器的方法

- › 用matlab设计的IIR滤波器源程序-IIR一阶低通/高通

- › 利用MATLAB增强MAX+PLUS II的仿真功能

- 在百度中搜索相关文章:用matlab来实现fpga功能的设计

- 在谷歌中搜索相关文章:用matlab来实现fpga功能的设计

- 在soso中搜索相关文章:用matlab来实现fpga功能的设计

- 在搜狗中搜索相关文章:用matlab来实现fpga功能的设计

当前位置:

当前位置: