��CPLDʵ��DSP��PLX9054֮�������

[11-20 16:14:15] ��Դ��http://www.88dzw.com FPGA �Ķ���8429��

����ժҪ���ȣУɿ��ڲ��������Ĵ������ֱ��ǿ��ƼĴ������ȣУɣã�����ַ�Ĵ������ȣУɣ��������ݼĴ������ȣУɣģ����������Ĵ�������ֱ�ӱ��������ʣ�����ÿִ��һ�ζԣãУ��ڲ��洢�ռ�ķ��ʶ������ȶԿ��ƼĴ����͵�ַ�Ĵ���д����Ӧ��ֵ��Ȼ����ܶ����ݼĴ������ж�д�������ȣУɿڵ��ⲿ�ӿ������������ߣȣĤ������������Լ�һ�������������Ϳ��ƣȣУɽӿڵĿ����ź���ɣ���Щ�����źŵľ����������£� �ȣãΣԣ�[��:��]�����ƣȣУɵIJ�������; �ȣȣףɣ̣�����ȷ�����룬���������������ֱ��ʾһ���ִ���ĵ�һ�����ֺ͵ڶ������֣� �ȣң��ף�����дѡ�� �ȣңģ٣�����״̬��־�� �ȣɣΣԣ��жϱ�־���ģӣ����������

��CPLDʵ��DSP��PLX9054֮�������,��ǩ��fpga��ʲô,fpga�̳�,http://www.88dzw.com

�ȣУɿ��ڲ��������Ĵ������ֱ��ǿ��ƼĴ������ȣУɣã�����ַ�Ĵ������ȣУɣ��������ݼĴ������ȣУɣģ����������Ĵ�������ֱ�ӱ��������ʣ�����ÿִ��һ�ζԣãУ��ڲ��洢�ռ�ķ��ʶ������ȶԿ��ƼĴ����͵�ַ�Ĵ���д����Ӧ��ֵ��Ȼ����ܶ����ݼĴ������ж�д�������ȣУɿڵ��ⲿ�ӿ������������ߣȣĤ������������Լ�һ�������������Ϳ��ƣȣУɽӿڵĿ����ź���ɣ���Щ�����źŵľ����������£�

�ȣãΣԣ�[��:��]�����ƣȣУɵIJ�������;

�ȣȣףɣ̣�����ȷ�����룬���������������ֱ��ʾһ���ִ���ĵ�һ�����ֺ͵ڶ������֣�

�ȣң��ף�����дѡ��

�ȣңģ٣�����״̬��־��

�ȣɣΣԣ��жϱ�־���ģӣ�����������жϣ�

�ȣ��ӣ������ַ�����ݸ������ߵ��������ַ��

�ȣģӣ����ȣģӣ����ȣãӣ�����ѡͨ���룬������Ͽ����ڲ���һ���ȣУ��ڲ�ѡͨ�źţȣӣԣңϣ£ţ�

�ȣӣԣңϣ£� ��[�Σϣԣ��ȣģӣ� �أϣ� �ȣģӣ���] �ϣ� �ȣãӣ�

����һ��д�ȣУɿڵIJ�����Ӧ����ʹ�ܣȣãӣ��仯�ȣģӣ���ȣģӣ�����ʹ�ȣӣԣңϣ£��źŲ���һ���½��أ��ȣУɿ�������½��ز��������źţȣãΣԣ̤������������ȣȣףɣ̺ͣȣң��ף�ͬʱ��ʹ�ܣȣãӵ�ͬʱ�ȳ��ȣңģ٣���ʹ��������ȴ�״̬��ֱ���ȣңģٲ����½��أ������ȣУɣ�����գ����Խ����µ����ݡ���ʱ�ȣӣԣңϣ£�Ҳ������һ�������أ��������ȣĤ������������ϵ����ݲ���������ȣУɣģ�����ɵ�һ�����ֵ�д�롣���ڵڶ������ֵ�д�룬���ڣ��������ģȣУɣ��Ѿ���գ�����ֱ��д�����ݣ��������δ���õ���������ԣȣңģ�һֱ����Ϊ�ͣ����һ���ֽڵ�д����ͬ���ò���Ҳ�ڣȣӣԣңϣ£ŵ��½��ز��������źţ����ڣȣӣԣңϣ£ŵ������ز����������ߣȣ�[��������]�����ݲ�����ȣУɣģ������һ������������д�������

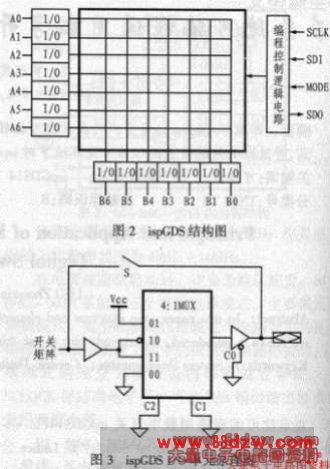

ͼ3

���ڶ��ȣУɵIJ��������ȣã���Ч�������������õ�ַ������ʽ�ӣȣУɣ�ִ�ж�����ʱ������壱�����ȣУɻ����ڲ���ַ������·��һ�������ȣãӵ��½��ؿ�ʹ�ȣңģٱ�Ϊ�ߵ�ƽ��ֱ���ڲ���ַ������·���������������ȣУɣģ��ȣңģٱ�Ϊ��Ч״̬Ϊֹ����ʱ�������ϵ�����Ϊ���������ݣ����Ҹ����ݽ�������Чֱ���ȣӣԣңϣ£������ز������ݺ�������ҡ������ڵڶ��ζ�������ʼʱ�������Ѿ������ڣȣУɣ����ˣ���ˣ��ڶ������ֵĶ���������������δ���õ�������ڣȣУɣ��Ե�ַ������ʽ���ж�����ʱ���ȣã�����������ֽڵĴ��������ʼ�ձ�����Ч��һ��������ڵĶ���������һ��ַ���������ϱ�ȡ������ˣ�������ڶ������ĵڶ������ֵĴ���֮���ڣȣӣԣңϣ£ŵĵڶ��������أ������ɣȣӣԣңϣ£ŵ��½��أ�ͨ���仯�ȣģӣ����ߣȣģӣ����������ȳ��ȣңģ��źţ�������ָʾ�ȣУ���æ�����ݵ�Ԥ��ȡ��

ͼ���ǣȣУɵĶ���дʱ��ͼ������ȣ���һֱ�Ӹߵ�ƽ��

�������ʵ��

��ϵͳ�УãУ̣ĵĹ�����Ҫ����ɣ����� �����˺ͣȣУɶ˿�֮������źź��������ߵ����ӣ�����֤���ݴ���Ŀɿ��ԡ�ͨ�����϶ԣ����� �����ͣȣУɶ�дʱ��ķ����ɼ���һЩ�ؼ��źţ���ȣãӡ��ңţ��ģ١��ȣңģٵ�ʱ����ƺ���Ҫ��ʵ���ϣ������ãУ̣���Ƶ���Ҫ����Ҳ��Χ���⼸���źŵ����չ���ġ�

ͼ4

�ɣȣãӡ��ȣģӣ��ͣȣģӣ���ͬ���ò����ģȣУɿ��ڲ��źţȣӣԣңϣ£ŵ������غ��½��أ�ֱ�ӿ���������ȣУɶ˿ڵ������źźͿ����źţ����ңȣӣԣңϣ£ű仯���ʾ��������ݴ�������ʣ��ɴ˿ɼ������ź���һ���dz��ؼ����źš�����ȣã��ź���Ϊ�ֽڴ����־�źţ�����һ�����ݴ���Ĺ�����ʼ�ձ�����Ч���������ݴ������֮���ȣã������ɿ��ƣȣңģ��źţ���ʹ��ָ�����ʼ״̬���Ӷ�Ϊ��һ�εĶ�д���������������ʱ�����ãȣģӣ���ȣģӣ��е�һ���̶������ߵ�ƽ����һ���������ƣȣӣԣңϣ£��Բ��������غ��½��ء����������ʱ���ȣģӣ��̶��Ӹߵ�ƽ�����ɣ��ģӺͣȣңģ��źŲ����������ƣȣģӣ��źš����ȣңģٴ�����Ч״̬�����ȣУɶ˿�δ��������ʱ���ȣģӣ��źŲ��䣬�������κ��źţ������ȣңģ���Чʱ���ȣģӣ��ź�ͬ���ģ��źű���һ�£����ڣ��ģӵ��½��ز��������źţ��������ز��������źš����⣬��һ�δ��俪ʼ֮ǰ�ͽ���֮�ȣģӣ���Ҫ����Ϊ�ߵ�ƽ��

- ��һƪ������FPGA��PCI���߽ӿ����

����CPLDʵ��DSP��PLX9054֮������ӡ��������

- › ��CPLDʵ�ֵ�Ƭ����ISA���߲���ͨ��

- › ��CPLDʵ��DSP��PLX9054֮�������

- › ��CPLDʵ�ֵ�Ƭ����дģ��

- �ڰٶ�������������£���CPLDʵ��DSP��PLX9054֮�������

- �ڹȸ�������������£���CPLDʵ��DSP��PLX9054֮�������

- ��soso������������£���CPLDʵ��DSP��PLX9054֮�������

- ���ѹ�������������£���CPLDʵ��DSP��PLX9054֮�������

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

��ǰλ�ã�

��ǰλ�ã�