����CPLD��ϵͳ��I2C���ߵ����

[11-20 16:14:01] ��Դ��http://www.88dzw.com FPGA �Ķ���8787��

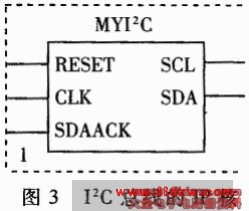

����ժҪ���ɼ��ãɣ�������ģ�����£�����������ֻʵ�ּ�д�Ͷ����������ֻ��д������ֻ��Ӳ�����Ե�ʱ����鷳Щ����д��ַ������û�о������ٲã��Ǻܼģɣ�������ϵͳ���ɴ��������ͼ����ʾ�ģɣкˡ����У��ңţӣţ�Ϊ��λ�źţ��ạ̃�Ϊϵͳʱ�ӡ� Ϊ���������淽�㣬��˫�������ߣӣģ��÷����������ģ�⣺�ӣģ�Ϊ����������ӣģ����ã�Ϊ�ӣģ���Ӧ���źš���������ɹ���ֻҪ�ѣӣģ�����Ϊ˫������һ�³���Ϳ�����ãУ̣��������أ�����ʵ��Ӧ�á� �ԣ��ģ��������ڲ���ַ�����ļĴ������г�ʼ�����ɣ��������ϴ����ʱ���ź�����Ϊ����ʼ�źţ��ӣ�����������ַ��д����λ���ӣ̣��ף����ڲ��Ĵ�������ַ���£���

����CPLD��ϵͳ��I2C���ߵ����,��ǩ��fpga��ʲô,fpga�̳�,http://www.88dzw.com

�ɼ��ãɣ�������ģ�����£�����������ֻʵ�ּ�д�Ͷ����������ֻ��д������ֻ��Ӳ�����Ե�ʱ����鷳Щ����д��ַ������û�о������ٲã��Ǻܼģɣ�������ϵͳ���ɴ��������ͼ����ʾ�ģɣкˡ����У��ңţӣţ�Ϊ��λ�źţ��ạ̃�Ϊϵͳʱ�ӡ�

Ϊ���������淽�㣬��˫�������ߣӣģ��÷����������ģ�⣺�ӣģ�Ϊ����������ӣģ����ã�Ϊ�ӣģ���Ӧ���źš���������ɹ���ֻҪ�ѣӣģ�����Ϊ˫������һ�³���Ϳ�����ãУ̣��������أ�����ʵ��Ӧ�á�

�ԣ��ģ��������ڲ���ַ�����ļĴ������г�ʼ�����ɣ��������ϴ����ʱ���ź�����Ϊ����ʼ�źţ��ӣ�����������ַ��д����λ���ӣ̣��ף����ڲ��Ĵ�������ַ���£��� ���������д�����ַ�����ݣ��ģ���ᣰ����д����һ��ַ���£��� ����������������ݣ��ģ���ᣱ����д���ַ���£��� ����������������ݣ��ģ���ᣲ����������д���ַ���£��� ������������������ݣ��ģ���ᣱ������ֹͣ�źţ��У���

��ԣ��ģ��������������·�еģ������ţ����������ӵ�Դ����ӣ̣��ף������������������������£��� ������������������������������ģ���ᣰ���ģ���ᣱ��������ʵ����Ҫд��ij�ʼ�����ݡ�

������ �ɣк˳���ı�д

���������ã֣ȣģ����Ա��ƣ��ӣã����ʱ�ӵ�����ǻ��ڣạ̃�����ʱ�ӵģ�����Ƶ�ġ�����������״̬��ɣ���ʼ���ӣԣ��ңԣ���ת�����ӣȣɣƣԣ���Ӧ�𣨣��ãˣ���״̬�������£�

������� ��������� ��� ����������������������룠��

������� �����ߣ�������� �����������

����������ֽ��̵�Դ�����Թ��ο���

������������ʼ�źŵIJ���

�Уңϣãţӣӣ����룠

��� ����'������� ���� ���룽����' ������

�ԣףãң����ģ��ԣ��ɣΦ�

�ӣạ̃�������'��

�����

�ԣףãң�����������������'����

���� ��榠

��� �ԣףãң��������������������� ������ �����ȽϼĴ����ԣףãҵĿ�ʼ

ֵ���ã����û�������

�ӣԣң£�������'��

���� ��榠

��� �ӣԣң£�����' ������ ������ʼ����

�ɣΣԣ����ɣΣԣ������������������� �����ɣΣ�Ϊʱ���������

��� �ɣΣԣ������������������� ������ ���������ӣģ����½���

�ӣģ���������'��

�����

�ӣģ���������'��

���� ��榠

��� �ɣΣԣ������������������� ������ �����ӣԣң¹飰����ֻ֤����

һ�ο�ʼ�ź�

�ӣԣң� ��������'��

�ɣΣԣ���������������������

���� ��榠

���� ��榠

�����еij�ʼ�����ݴ�����Ϻ���ֹͣ�źţ����������������ƣ��ڴ�ʡ�ԡ�

���������� ����ת������

����ת�����̲�����λ���䣬���䣸λ֮����Ӧ��״̬��

������ ����������

��� ���������������������� ������ �����������������������

������CPLD��ϵͳ��I2C���ߵ���ơ��������

- › ����CPCI���ߵĶ����ڿ����

- › һ�ֻ���CPLD���������źŴ���ϵͳ���

- › ����CPLD�ij�����Դ����ϵͳ����Ӳ�����

- › ����CPLD��FPGA��CMI���������ʵ��

- › ����CPLD��ѹ�����ﴫ��������·���

- › ����CPLD��CCD�źŷ��������о�

- �ڰٶ�������������£�����CPLD��ϵͳ��I2C���ߵ����

- �ڹȸ�������������£�����CPLD��ϵͳ��I2C���ߵ����

- ��soso������������£�����CPLD��ϵͳ��I2C���ߵ����

- ���ѹ�������������£�����CPLD��ϵͳ��I2C���ߵ����

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

��ǰλ�ã�

��ǰλ�ã�