基于FPGA的USB2.0控制器设计

[11-20 16:13:52] 来源:http://www.88dzw.com FPGA 阅读:8631次

文章摘要:在需要读取SRAM中的数据(tx_dma_en=1)时,DMA仲裁器由IDIE状态进入MEM_RD1状态,读取4字节数据到发送缓冲区中,然后进入状态MEM_RD2,再读4字节进入状态MEM_RD3,这8字节轮流使用Buffer0和Buffer1缓冲区:在需要读取SRAM中的数据(tx_dma_en=1)时,DMA仲裁器由IDLE状态进入MEM_RD1状态,读取4字节数据到发送缓冲区中,然后进入状态MEM_RD2,再读4字节进入状态MEM_RD3,这8字节轮流使用Buffer0和Buffer1缓冲区:if((NOT adr_cb[2]) AND mackthen Buffer0<=SRAM

基于FPGA的USB2.0控制器设计,标签:fpga是什么,fpga教程,http://www.88dzw.com在需要读取SRAM中的数据(tx_dma_en=1)时,DMA仲裁器由IDIE状态进入MEM_RD1状态,读取4字节数据到发送缓冲区中,然后进入状态MEM_RD2,再读4字节进入状态MEM_RD3,这8字节轮流使用Buffer0和Buffer1缓冲区:

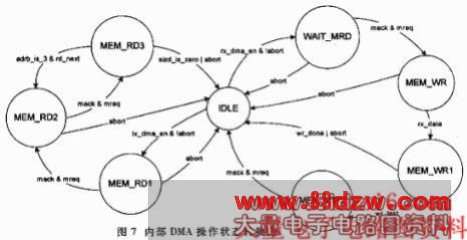

在需要读取SRAM中的数据(tx_dma_en=1)时,DMA仲裁器由IDLE状态进入MEM_RD1状态,读取4字节数据到发送缓冲区中,然后进入状态MEM_RD2,再读4字节进入状态MEM_RD3,这8字节轮流使用Buffer0和Buffer1缓冲区:

if((NOT adr_cb[2]) AND mack

then Buffer0<=SRAM_DATA_I;

elsif (adr_cb[2] AND mack)

then Buffer1<=SRAM_DATA_I;

end if;

在MEM_RD3状态判断是否还需要读下一个数据,如果需要再进入状态MEM_RD2,否则在传输完所有字节后,返回到IDLE状态。在发送数据过程中,使用14bit计数器sizd_c决定传输字节数,取自Ep_BUF[30:17],每发送1字节数据,它的值减1。在图7中的各个状态中,由于超时、CRC校验错误或得到的数据发生错误时,PE产生的Abort信号会使当前状态都回到IDLE。

文中阐述了USB2.0功能控制器的一种实现方案。 其VHDL语言实现代码,已在XILINX公司的FPGA Virtex XVV3006fg456中通过了Xilinx ISE的仿真、综合及布局布线。FPGA的规模是32万门,1536个CLB(可配置逻辑单元)。该控制模块占用2050个Slice(66%),使用了1697个Slice触发器(27%)和3047个4输入LUT表(49%)。整个FPGA的速度可达到56.870MHz,完全满足视频数据的高速传输(对32bit数据操作,达到480Mb/s的速度时钟只需15MHz)。该方案实现的控制器便于修改且易于实现,可作为一个功能模块嵌入到SOC中,可使不同情况最大限度地灵活设计片上系统。

《基于FPGA的USB2.0控制器设计》相关文章

- › 基于FPGA的单片彩色LCD投影机设计

- › 256级灰度LED点阵屏显示原理及基于FPGA的电路设计

- › 基于FPGA的LCD%26amp;VGA控制器设计

- › 基于FPGA的信道化接收机

- › 基于FPGA和SMT387的SAR数据采集与存储系统

- › 基于FPGA的栈空间管理器的研究和设计

- 在百度中搜索相关文章:基于FPGA的USB2.0控制器设计

- 在谷歌中搜索相关文章:基于FPGA的USB2.0控制器设计

- 在soso中搜索相关文章:基于FPGA的USB2.0控制器设计

- 在搜狗中搜索相关文章:基于FPGA的USB2.0控制器设计

当前位置:

当前位置: