I2C�����ӿ�IP�˵�CPLD���

[11-20 16:13:28] ��Դ��http://www.88dzw.com FPGA �Ķ���8268��

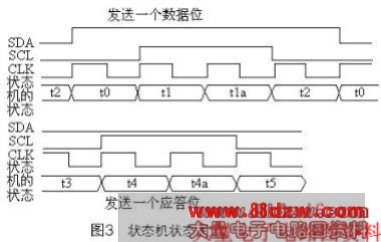

����ժҪ�����³����У�Cmd_reg2Ϊ���������ݴ�λ��Sh_reg[]Ϊ�������棬ͨ�����ƣ����λ����Sh_reg7Ϊ��ǰ���������ݣ�����SDA_tmp ��ͨ��ͼ 3���ճ����Կ�������һ������״̬������λ����ϸ���̡������嵥���£�IF Cmd_reg2 THEN --��"��������"����Sh_reg7��Ϊ��ǰ����λSDA_tmp = Sh_reg7;ELSESDA_tmp = VCC;END IF;St.clk = SysClk;St.ena = BaudGen;CASE St IS --���ƴ���8λ���ݵ�״̬��WHEN t0 =>IF Cmd_reg2 OR Cmd_r

I2C�����ӿ�IP�˵�CPLD���,��ǩ��fpga��ʲô,fpga�̳�,http://www.88dzw.com

�������³����У�Cmd_reg2Ϊ���������ݴ�λ��Sh_reg[]Ϊ�������棬ͨ�����ƣ����λ����Sh_reg7Ϊ��ǰ���������ݣ�����SDA_tmp ��ͨ��ͼ 3���ճ����Կ�������һ������״̬������λ����ϸ���̡������嵥���£�

IF Cmd_reg2 THEN --��"��������"����Sh_reg7��Ϊ��ǰ����λ

SDA_tmp = Sh_reg7;

ELSE

SDA_tmp = VCC;

END IF;

St.clk = SysClk;

St.ena = BaudGen;

CASE St IS --���ƴ���8λ���ݵ�״̬��

WHEN t0 =>

IF Cmd_reg2 OR Cmd_reg3 THEN

SDA = SDA_tmp; --��ʼ��������

SCL = GND;

St = t1;

ELSE

St = t0;

END IF;

WHEN t1 =>

SCL = VCC;

SDA = SDA_tmp;

St = t1a;

WHEN t1a =>

SCL = VCC;

SDA = SDA_tmp;

St = t2;

WHEN t2 =>

Sh_reg[7..1] = Sh_reg[6..0]; --�������ƣ�ȡ��λ

Sh_reg[0] = GND;

Sh_reg[].ena = EXU;

SCL = GND;

SDA = SDA_tmp;

IF Bit[] == 7 THEN --��8λ���꣬��Ӧ��λ���������

St = t3;

ELSE

St = t0;

END IF;

WHEN t3 => --��Ӧ��λ

SDA =GND;

St = t4;

WHEN t4 =>

SDA = GND;

SCL = VCC;

St = t4a;

WHEN t4a =>

SDA = GND;

SCL = VCC;

St = t5;

WHEN t5 =>

SCL = GND;

St = t6;

WHEN t6 =>

SDA = GND;

FINISHED = VCC;

St = t0;

END CASE;

Bit[] = Bit[] + 1; �D�D--������һλ���Ѵ���λ����һ

����ͼ 4Ϊ����������ʼ�źŸ����Ժ���2��8λ���ݣ�ÿ�����ݺ��һ��Ӧ��λ�����������һ������Ҫ�������£���ͣһ��ʱ�䣬�����͵ڶ������ݣ�2�����������Ժ���������ֹͣ����Ҫ������ֹͣ�źš���Щ�źţ���SDA��SCL����ȫ����I2C��ʱ��Ҫ��Ҫʹ���ߴ������ʴﵽ�Ľ���Ĺ淶����400 kb/s����Ϊ��������������ÿ����1λ������Ҫ4��ʱ�����ڣ�����������ʱ��Ϊ1600 kHz��ͼ4��ExecuteΪִ���źţ�����Ϊ�ߵ�ƽʱ����������DIN[7..0]��Ч��EXUΪ����ʹ���źţ�ֻ�е���Ϊ�ߵ�ƽʱ���������ʹ������ݵ���Χ������StartΪ��ʼ�����źţ����ڷ�����ʼ�źţ�STOP���ڸ�֪�������ݴ������������ֹͣ�źš�

���������Ժ�ͨ����̵��½����ɵ�pof�ļ���ISP(��ϵͳ���)��ʽ���ص�FPGA��EPM7128SLC84-6��I/O��SDA��SCL���������裬�����ƬI2C����SAA1064(LED��ʾI2C���벢��оƬ)���в��ԣ����CPLD���ø�I2C��IP�ˣ�����������������Ҫ����ʾ��

�����

1 Altera. ALTERA DIGITAL LIBRARY 2000

2 ������. ��Ƭ�����̳�. �������������պ����ѧ������, 2000

3 �����. �ɱ��������ԭ����������Ӧ��. �������ӿƼ���ѧ������, 2000

4 SAA1064 Product Specification Philps.

- ��һƪ������SRAM�Ŀ������õ�·

��I2C�����ӿ�IP�˵�CPLD��ơ��������

- › TI �Ƴ���������õ�I2C����

- › I2C�����ӿ�IP�˵�CPLD���

- �ڰٶ�������������£�I2C�����ӿ�IP�˵�CPLD���

- �ڹȸ�������������£�I2C�����ӿ�IP�˵�CPLD���

- ��soso������������£�I2C�����ӿ�IP�˵�CPLD���

- ���ѹ�������������£�I2C�����ӿ�IP�˵�CPLD���

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

��ǰλ�ã�

��ǰλ�ã�