C8051F��80C51ϵ�е�Ƭ���IJ�ͬ��ʼ��

[09-11 23:03:01] ��Դ��http://www.88dzw.com ��Ƭ��ѧϰ �Ķ���8631��

����ժҪ�������濪�����üĴ����أ£ң����أ£ң��ͣأ£ң�������Ķ�Ӧλ�����ó�����ʱ�����濪�ؽ��˿����ŷ�������裻���һ���������������λδ�����ó�����������˿ڲ���ͨ�����ŷ��ʡ�δ�����õĽ��濪�ط���˿ڿɵ����������ģɣ��Ͽ�ʹ�á���ϵͳ��λ��Ĭ�ϵļĴ����أ£ң����أ£ң��ͣأ£ң���ֵ��Ϊ�㣬�����Уɣ������ű�ǿ�ȳ�����ڣ������������Ҳ����ڲ���Դ��ͨ��������û�������ϵͳ��Ȼ�����壬���ԣ�������ζ�Ӧ�ãأ£ң��ĵڣ�λΪ����ʹ���濪�������Ա���������źš������� ϵͳʱ��Դ�ã��������ƣ����ص�ϵͳʱ�ӿ���ȡ���ڲ���·���ⲿ��·���������ң����մ�г���·��������У̵̣�

C8051F��80C51ϵ�е�Ƭ���IJ�ͬ��ʼ��,��ǩ����Ƭ������,��Ƭ��ԭ��,��Ƭ���̳�,http://www.88dzw.com�����濪�����üĴ����أ£ң����أ£ң��ͣأ£ң�������Ķ�Ӧλ�����ó�����ʱ�����濪�ؽ��˿����ŷ�������裻���һ���������������λδ�����ó�����������˿ڲ���ͨ�����ŷ��ʡ�δ�����õĽ��濪�ط���˿ڿɵ����������ģɣ��Ͽ�ʹ�á���ϵͳ��λ��Ĭ�ϵļĴ����أ£ң����أ£ң��ͣأ£ң���ֵ��Ϊ�㣬�����Уɣ������ű�ǿ�ȳ�����ڣ������������Ҳ����ڲ���Դ��ͨ��������û�������ϵͳ��Ȼ�����壬���ԣ�������ζ�Ӧ�ãأ£ң��ĵڣ�λΪ����ʹ���濪�������Ա���������źš�

���������� ϵͳʱ��Դ

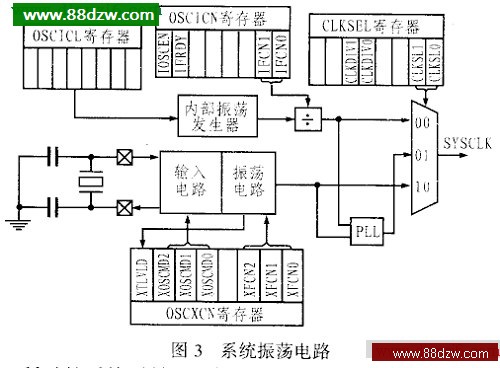

�ã��������ƣ����ص�ϵͳʱ�ӿ���ȡ���ڲ���·���ⲿ��·���������ң����մ�г���·��������У̵̣�·������У̵̣�·������Դ��ѡ�������ڲ���·��Ҳ����ѡ���ⲿ��·��ͨ���У̵̣ı�Ƶ���ÿ������ʱ��Ƶ�ʡ��ã��������ƣ�����ϵͳ�ڵ���·��ͼ����ʾ��Ҫ���������ϵͳʱ�ӣ�ͨ��Ҫ���ã����Ĵ������ϣӣãأɣΡ��ϣӣãɣãΡ��ϣӣãɣã̡��ạ̃ˣӣţ̡��У̣̣ϣãΡ��У̣̣ϣƣ̣ԡ��У̣̣��ģɣ֡��У̣̣��ͣգ̣����к����йأУ̵̣ļĴ�����

������ ����ܼĴ����ӣƣҽṹ

��ͣãӡ������ģӣƣҲ�ͬ���ǣ��ã��������ƣ����صģӣƣ���ͼ����ʾ�Ķ�ҳ��ɣ����У�ҳ��ҳ��Ϊ���������������������������ӣƣҷֲ��ڲ�ͬ��ҳ���أ£ң����أ£ң����أ£ң����ϣӣãأɣΡ��ϣӣãɣãΡ��̣̣ϣãΡ��У̣̣ϣƣ̣Եȶ�λ�ڣ���ҳ���ʱ���йصļĴ����ԣãϣΡ��ԣͣϣġ��ԣȡ��ԣ̵ȶ�λ�ڣ�ҳ��ڶ�д�����ӣƣ�֮ǰ���������л�����Ӧ��ҳ����ʹ�á��ͣϣ� �ӣƣңУ��ǣţ���ҳ�š�ָ���������л��������ӣƣ�������Щҳ����鿴��ص����ϡ�

�� Ӧ�þ���

������Ҫ�õ���������һ�������첽ͨ�ţգ��ңԺ�һ�����жϣɣΣԣ�������ϵͳĬ�ϵ�����˳�У��ڱ��ڲ���Դ������ռ�ã����УУ�����Ϊ�գ��ң�ͨ�ŵģңضˣ� �У�����Ϊ�գ��ң�ͨ�ŵģԣضˣ��У�����Ϊ���жϣɣΣԣ��������ţ������˿�Ϊͨ�ãɣ��Ͽڡ��У���Ϊ�����������������ڣ��У���Ϊͨ�����������ڣ��У���Ҳ��ͨ����������ڡ��������£�

���������壨�㣸�������棱���������㣩

�ϣң� ������

�ʣͣ� �ңţӣţ� ���������

�ϣң� ������

�ʣͣ� �ţ�_�ɣΣ� �����жϣɣΣԣ����

�ϣң� ���£�

�ʣͣ� �ԣɣͣ�_�� ����ʱ�����ж����

�ϣң� ��������

�ңţӣţԦ��ͣϣ֣� �ףģԣãΣ������ģţ� ����ֹ���Ź�

�ͣϣ� �ףģԣãΣ��������ģ�

�ͣϣ� �ӣƣңУ��ǣţ� �����ƣ� ��ȡ����ܼĴ����ģ���ҳ

�ͣϣ� �ϣӣãأãΣ��������������������� ������ʱ��Դѡ���壬Ƶ�ʷ�Χ�ڣ����ͣȣ�����

�ϣң� �У̣̣��ãΣ��������������������� �����ⲿ������Ϊ�У̵̣�Դ

�ͣϣ� �У̣̣��ģɣ֣��������������������� ���У̵̣������ϵ��������λ��Ĭ�ϣ�

- ��һƪ��8098��Ƭ�����Ͻ���

��C8051F��80C51ϵ�е�Ƭ���IJ�ͬ��ʼ�����������

- › оƬ���ż���Ҫ����MC68HC805C4 8λ������(A/D)

- › оƬ���ż���Ҫ����MC68HC805B6 8λ������(A/D)

- › 74ϵ�����ֵ�·74HC805����2��������������

- › C8051F EC2 JTAG��������·ͼ

- › C8051F340��USBXpress������USBͨ�����

- › Silicon Laboratories�Ƴ�C8051F336ϵ�и�����8λ������

- �ڰٶ�������������£�C8051F��80C51ϵ�е�Ƭ���IJ�ͬ��ʼ��

- �ڹȸ�������������£�C8051F��80C51ϵ�е�Ƭ���IJ�ͬ��ʼ��

- ��soso������������£�C8051F��80C51ϵ�е�Ƭ���IJ�ͬ��ʼ��

- ���ѹ�������������£�C8051F��80C51ϵ�е�Ƭ���IJ�ͬ��ʼ��

- ���칦��

- ��Ƭ��ѧϰ

- ��س����

- ��ѹ��Դ

- �Զ�����

- ����������

- �ƹ���Ƶ�·

- ��·���

- PCB���

- CAD CAM

- ����ư�

- ��е�ӹ�

- ʴ����ӡ

- �Ʋ�Ϳ��

- ��·����Ƭ

- ��ҵ��

- �繤����֪ʶ

- ��������

- ��������

- ���ӻ���֪ʶ

- �������

- ��ȫ����֪ʶ

- ¥�����

- ���ӵ�

- ���ܽ���

- �ۺϲ���

- ��Ϣ��ʾ���缼��

- �ӿڶ���

- �����

- EDA/PLD

- ��������EMC

- ������

- ��·����

- ���ɵ�·

- RF��Ƶ

- armǶ��ʽ

- ��Դ����

- FPGA

- ���Ƽ���

- Ƕ��ʽϵͳ

- ģ����Ӽ���

- �������

- ���ӵ�·ͼ

- ��������

- �� Microchip��Ƭ��ϵ������12λADC����

- �� Microchip����2 MHz����������

- �� ��8051��Ƭ��Ӧ��ϵͳ��ʹ��DiskOnChip

- �� Microchip��12��ȫ�¸�����8λ���浥Ƭ��

- �� AT91ϵ���������������̵ķ�����ʵ��

- �� 16λ������L80C186-10���Լ����о�

- �� NCP5381˫Ե�������ٻ��յ��ӡ���Top 1

- �� �Ƴ��Լ��Ļ���x86�Ķ���Ƕ��ʽϵͳ(��)

- �� X86��������Ƕ��ʽӦ���е�������

- �� һ�ֻ���C51�Ķ�������Ƽ�Ӧ��

��ǰλ�ã�

��ǰλ�ã�